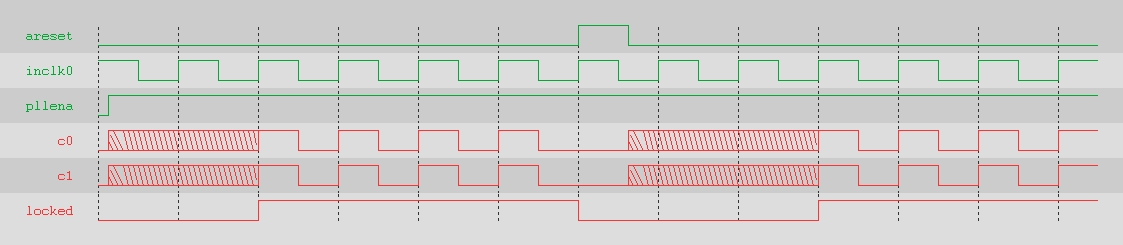

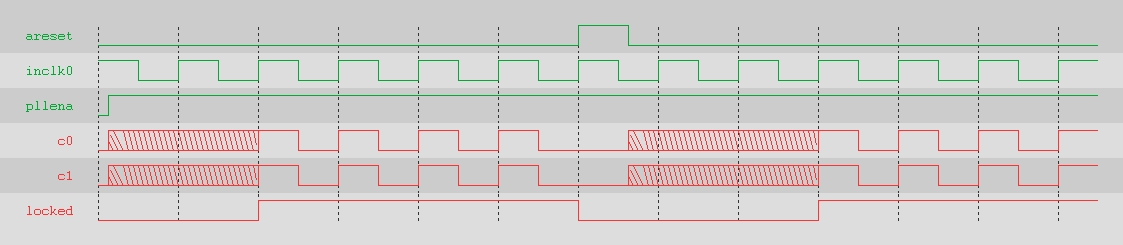

The following waveforms show the behavior of altpll megafunction for the chosen set of parameters in design pll.v. The design pll.v has Cyclone II PLL_TYPE pll configured in NORMAL mode The primary clock input to the PLL is INCLK0, with clock period 20000 ps. Output port LOCKED will go high when the PLL locks to the input clock.

When input port ARESET is asserted, it will cause the LOCKED port and all CLK outputs to drop to zero. The PLL will relock to the input clock when this port is deasserted. When input port PLLENA is deasserted, it will cause the PLL to unlock, and the LOCKED port and all CLK outputs will drop to zero.